Характеристики

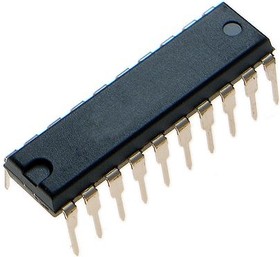

SN74ALS273N, DIP20 0/+70 CThe SN74ALS273N is an octal positive-edge-triggered D-type Flip-flop with clear and single-rail outputs. It utilizes TTL circuitry to implement D-type flip-flop logic with a direct-clear (CLR) input. Information at the data (D) inputs meeting the setup-time requirements is transferred to the Q outputs on the positive-going edge of the clock pulse. Clock triggering occurs at a particular voltage level and is not directly related to the transition time of the positive-going pulse. When CLK is at either the high or low level, the D input signal has no effect at the output.

• Buffered clock and direct-clear inputs

• Individual data input to each flip-flop

Личный кабинет

Личный кабинет

Загрузка

Загрузка