Характеристики

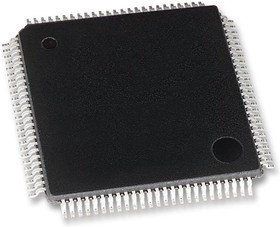

LPC1763FBD100,551The LPC1763FBD100.551 is a 32-bit Microcontroller based on ARM Cortex-M3 core with RISC architecture operates at a maximum frequency of 100MHz. The ARM Cortex-M3 is a next generation core that offers system enhancements such as enhanced debug features and a higher level of support block integration. The ARM Cortex-M3 CPU incorporates a 3-stage pipeline and uses a Harvard architecture with separate local instruction and data buses as well as a third bus for peripherals. The ARM Cortex-M3 CPU also includes an internal prefetch unit that supports speculative branching. The device incorporates 256kB internal flash, 64kB internal RAM, 8-channel general purpose DMA controller, 8-channel 12-bit A/D converter, 10-bit D/A converter, motor control PWM, quadrature encoder interface, four general purpose timers, 6-output general purpose PWM, ultra-low power real-time clock (RTC) with separate battery supply and 70 general-purpose I/O pins.

• ARM Cortex-M3 built-in nested vectored interrupt controller (NVIC)

• In-system programming (ISP) and In-application programming (IAP)

• Multilayer AHB matrix interconnect

• Split APB bus

• Standard JTAG debug interface for compatibility

• Emulation trace module enables non-intrusive, high-speed real-time tracing of instruction execution

• Integrated PMU (power management unit)

• Four reduced power modes — Sleep, deep-sleep, power-down and deep power-down

• Four external interrupt inputs configurable as edge/level sensitive

• Non-maskable Interrupt (NMI) input

• The wake-up interrupt controller (WIC)

• Brownout detect with separate threshold for interrupt and forced reset

• Power-on reset (POR)

• Crystal oscillator with an operating range of 1MHz to 25MHz

• 4MHz Internal RC oscillator trimmed to 1 % accuracy

• PLL allows CPU operation up to the maximum CPU rate

• USB PLL for added flexibility

• Code read protection (CRP) with different security levels

• Unique device serial number for identification purposes

Микросхемы / Микроконтроллеры / Микроконтроллеры NXP

Корпус: 100-LQFP (14×14), инфо: 32-bit LPC1700 ARM Cortex M3 RISC 256KB Flash 3.3V

Личный кабинет

Личный кабинет

Загрузка

Загрузка