Компания Imec разработала новую архитектуру ячеек DRAM, в которой реализованы два тонкопленочных транзистора из индия-галлия-цинка (IGZO-TFT) и без накопительного конденсатора. Ячейки DRAM в этой конфигурации 2T0C (2 транзистора 0 конденсатора) показывают время удерживания более 400 с для различных размеров ячеек, что значительно снижает частоту обновления памяти и энергопотребление.

Возможность обрабатывать IGZO-TFT во внутренней линии (BEOL) уменьшает занимаемую ячейкой площадь и открывает возможность объединения отдельных ячеек. Эти революционные результаты открывают путь к созданию монолитной памяти 3D-DRAM с низким энергопотреблением и высокой плотностью.

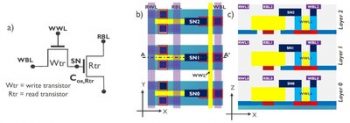

(a) Схема ячейки 2T0C DRAM, где запоминающим элементом является оксидная емкость Cox транзистора чтения; (b) пример схематического вида сверху массива 2T0C DRAM на единственном плоском уровне. Направление поперечного сечения A-A ‘указывает на то, что плотность массива может быть увеличена путем (c) наложения нескольких слоев ячейки 2T0C.

Масштабирование традиционной памяти DRAM 1T1C (один транзистор — один конденсатор) за пределы плотности кристалла 32 ГБ сталкивается с двумя основными проблемами. Во-первых, трудности с масштабированием матричных транзисторов на основе кремния затрудняют поддержание необходимого тока отключения и сопротивления мировой линии при уменьшении размера ячейки. Во-вторых, трехмерная интеграция и масштабируемость — окончательный путь к DRAM высокой плотности — ограничиваются необходимостью накопительного конденсатора. Imec представляет новую архитектуру DRAM, которая отвечает на обе проблемы, тем самым предлагая путь масштабирования к маломощной памяти 3D-DRAM высокой плотности.

В новой архитектуре реализованы два IGZO-TFT, которые хорошо известны своим очень низким током отключения, и без накопительного конденсатора. В этой конфигурации 2T0C паразитная емкость считывающего транзистора служит запоминающим элементом. Полученные в результате ячейки DRAM демонстрируют время удерживания> 400 с благодаря чрезвычайно низкому (извлеченному) отключенному току 3 × 10-19 А / мкм.

Эти прорывные результаты были получены для оптимизированных масштабированных IGZO-транзисторов (с длиной затвора 45 нм), обработанных на пластинах диаметром 300 мм. Оптимизация была направлена на подавление влияния кислородных и водородных дефектов как на ток, так и на пороговое напряжение — одну из основных задач при разработке IGZO-TFT.

Гури Санкар Кар, программный директор imec: «Помимо длительного времени хранения, ячейки DRAM на основе IGZO-TFT обладают вторым важным преимуществом перед существующими технологиями DRAM. В отличие от Si, транзисторы IGZO-TFT могут изготавливаться при относительно низких температурах и, таким образом, совместимы с обработкой BEOL. Это позволяет нам перемещать периферию ячейки памяти DRAM под массивом памяти, что значительно сокращает занимаемую площадь кристалла памяти. Кроме того, обработка BEOL открывает пути к наложению отдельных ячеек DRAM, что позволяет создавать архитектуры 3D-DRAM. Наше революционное решение поможет разрушить так называемую стену памяти, позволяя памяти DRAM продолжать играть решающую роль в ресурсоемких приложениях, таких как облачные вычисления и искусственный интеллект ».

Личный кабинет

Личный кабинет

Загрузка

Загрузка